Theory

Introduction

Interrupts are a fundamental concept in computer systems that allow the processor to respond immediately to external or internal events, temporarily halting the normal program flow to execute a specific function known as the Interrupt Service Routine (ISR). Once the ISR is completed, the processor resumes the interrupted program seamlessly. Interrupt handling ensures efficient and real-time responses to critical tasks, making it an essential feature of microcontrollers and processors.

Figure-1: Interrupt handler

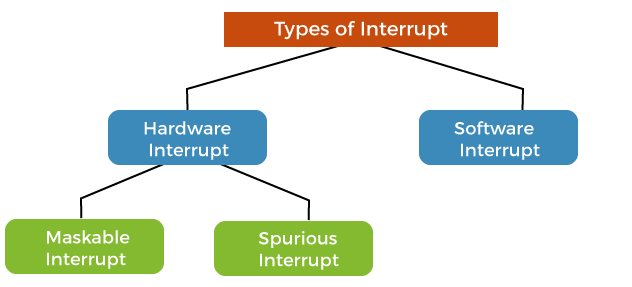

Types of Interrupts:

1.Hardware Interrupts:Triggered by external devices

(e.g., keyboards, timers, sensors) sending a signal to the

processor.

2.Software Interrupts: Triggered programmatically by instructions

in the code (e.g., system calls).

Figure-2: Types of Interrupt

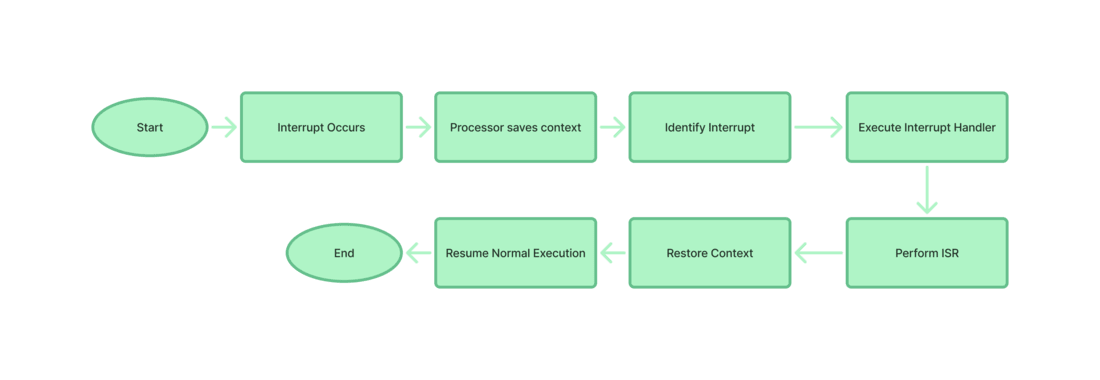

Interrupt Handling Mechanism

The interrupt handling mechanism involves the following steps:

1. Interrupt Request (IRQ): An interrupt signal is generated by an external or internal source.

2. Interrupt Acknowledgment: The processor detects the interrupt and completes the current instruction execution.

3. Context Saving: The processor saves the current program state (registers, program counter, etc.) to allow resumption later.

4. Interrupt Service Routine (ISR): The processor jumps to a predefined memory location to execute the ISR, which handles the interrupt event.

5. Context Restoration: After the ISR execution, the saved state is restored.

6. Return to Main Program: The processor resumes the interrupted task seamlessly.

Figure-3: Flowchart of Interrupt Handling Mechanism

Managing Multiple Devices

When more than one device raises an interrupt request signal,

then additional information is needed to decide which device to be

considered first. The following methods are used to decide which

device to select: Polling, Vectored Interrupts, and Interrupt Nesting.

• Polling: In polling, the first device encountered

with the IRQ bit set is the device that is to be serviced first.

Appropriate ISR is called to service the same. It is easy to implement

but a lot of time is wasted by interrogating the IRQ bit of all

devices.

• Vectored Interrupts: In vectored interrupts, a

device requesting an interrupt identifies itself directly by sending a

special code to the processor over the bus. This enables the processor

to identify the device that generated the interrupt. The special code can

be the starting address of the ISR or where the ISR is located in memory

and is called the interrupt vector.

• Interrupt Nesting: In this method, the I/O device

is organized in a priority structure. Therefore, an interrupt

request from a higher-priority device is recognized whereas a

request from a lower-priority device is not. The processor accepts

interrupts only from devices/processes having priority.

Figure-4: Methods for managing multiple devices

Interrupt Latency

Interrupt latency is the time delay between the occurrence of an interrupt signal and the start of the execution of the corresponding interrupt service routine (ISR). It encompasses the time taken by the processor to recognize the interrupt, complete the current instruction, save the necessary state, and begin executing the ISR. Minimizing interrupt latency is crucial in real-time systems where timely response to external events is essential for maintaining system stability and performance.

Benefits of Interrupts:

• Real-time Responsiveness: Interrupts permit a

system to reply promptly to outside events or signals, permitting

real-time processing.

• Efficient Resource usage: Interrupt-driven

structures are more efficient than system that depend on

busy-waiting or polling strategies. Instead of continuously

checking for the incidence of event, interrupts permit the

processor to remain idle until an event occurs, conserving

processing energy and lowering energy intake.

• Multitasking and Concurrency: Interrupts allow

multitasking with the aid of allowing a processor to address

multiple tasks concurrently.

• Improved system Throughput: By coping with

occasions asynchronously, interrupts allow a device to overlap

computation with I/O operations or other responsibilities,

maximizing system throughput and universal overall performance.

Components Used:

• D Flip-Flop A D flip-flop (DFF) helps in detecting and managing interrupt

signals in a circuit. When an external event triggers an interrupt, the D flip-flop stores

the signal and passes it to the system at the right time, preventing errors. It ensures

the interrupt signal is stable and not lost, especially if it arrives at an unexpected

moment. It also helps remove unwanted noise from buttons or sensors. In testing, a D

flip-flop makes it easier to check if the system correctly detects and responds to

interrupts. This makes the circuit more reliable and efficient.

• Multiplexer: A multiplexer (MUX) is a combinational logic

circuit that selects one of several input signals and forwards it to the output based on

the select lines. It acts as a data selector, allowing multiple data sources to share a

single communication channel.

• Logic Gates: Logic gates are the basic building blocks of digital

circuits. They perform logical operations on binary inputs (0s and 1s) to produce a binary

output. Each gate follows a specific truth table based on Boolean algebra.

Types of Logic Gates:

• And Gate: Outputs 1 only if all inputs are 1.

• OR Gate: Outputs 1 if at least one input is 1.

• NOT Gate: Inverts the input (0 becomes 1, 1 becomes 0).

• NAND Gate: Outputs 0 only if all inputs are 1.

• And Gate: Outputs 1 only if all inputs are 0.

• XOR Gate: Outputs 1 if inputs are different.

• XNOR Gate: Outputs 1 if inputs are the same.

Importance of Interrupt Handling

Interrupts are critical in real-time systems where events need immediate

attention. They allow efficient multitasking, as the processor can switch

from routine tasks to critical ones without polling for events, saving

computational resources.Here's why it is important:

• Without interrupts, the CPU would have to constantly check (poll)

peripherals for their status, wasting valuable processing time.

• Interrupts enable systems to respond promptly to critical events

(e.g., pressing a key, receiving data over a network, or a hardware fault).

• Interrupts can be prioritized, ensuring critical tasks are handled first.

• Interrupts facilitate context switching between tasks in multi-tasking operating systems.

• In battery-powered devices, interrupt-driven designs enable the CPU to enter low-power states

and wake up only when required.

• Interrupts can handle errors or unexpected conditions in hardware or software

(e.g., divide-by-zero errors, invalid memory access).